半桥中点负压及应对策略

发布时间:2024-09-18

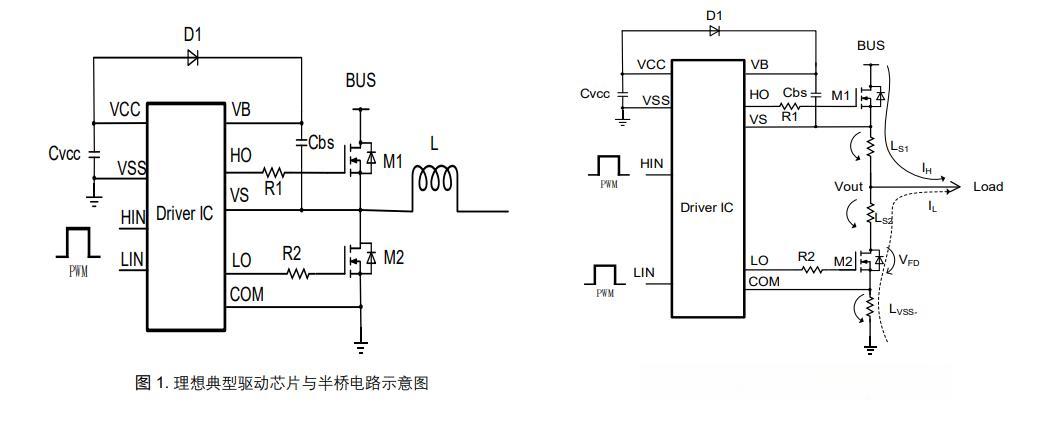

在电力电子电路中,半桥结构是一种常见的拓扑。然而,在实际应用中,半桥中点往往会出现负压现象,这不仅会影响电路的正常工作,还可能导致驱动芯片损坏。本文将深入探讨半桥中点负压的产生原因、影响因素以及应对策略。

半桥中点负压的产生原理

半桥中点负压主要由寄生电感和电流变化率共同作用产生。在半桥电路中,当上管关断、下管开通的瞬态切换过程中,由于线路中存在寄生电感,会在寄生电感中产生压降,导致半桥中点(VS端)电压低于地电位(VSS),从而形成负压。

具体来说,负压的大小可以通过以下公式估算:

VS - VSS = -VFD - (LVSS + LS2) × dIL/dt - LS1 × dIH/dt

其中,VFD为二极管正向压降,LVSS和LS2为寄生电感,dIL/dt和dIH/dt分别代表电流变化率。这个公式表明,电流变化率越大,寄生电感越大,负压也就越大。

影响半桥中点负压的关键因素

-

电流变化率(di/dt):在开关瞬间,特别是短路情况下,电流变化率急剧增加,会导致更大的负压。

-

寄生电感:包括器件本身的寄生电感和PCB走线的寄生电感。这些寄生电感在高di/dt情况下会产生额外的压降,加剧负压现象。

-

PCB布局:合理的PCB布局可以有效降低寄生电感,从而减小负压。例如,将上下功率管尽量靠近摆放,驱动芯片靠近被驱动的功率管,都可以减少寄生电感。

应对半桥中点负压的有效策略

-

优化PCB布局:这是降低负压最有效的方法之一。通过合理布局,可以显著减少寄生电感,从而降低负压。

-

增加驱动电阻:适当增加驱动电阻可以降低di/dt,从而减小负压。但需要注意的是,过大的驱动电阻会增加开关损耗,影响效率。

-

使用钳位电路:在VS端和地之间加入二极管和稳压管串联的钳位电路,可以限制负压的大小。例如,使用二极管串联3.3V稳压管的钳位方案,在85V~290V 1000W源跳变测试中,有效防止了PFC炸机现象。

-

改善自举电路:对于采用自举方式的驱动电路,选择合适的自举电容和二极管,可以提高电路的抗干扰能力,间接降低负压的影响。

-

增加解耦电容:在驱动芯片的VB和VS脚之间增加1uF的解耦电容,可以有效抑制Vb产生的负压,防止芯片失效。

结语

半桥中点负压是电力电子电路设计中不可忽视的问题。通过深入理解其产生原理,合理设计电路布局,选用合适的元器件,我们可以有效应对这一挑战,确保电路的稳定可靠运行。在实际应用中,还需要根据具体情况进行综合权衡,找到最佳的解决方案。