拉电阻和下拉电阻作用、区别及应用

发布时间:2024-09-16

在数字电路设计中,拉电阻和下拉电阻是两个不可或缺的重要元件。它们虽然名称相似,但功能和应用却大不相同。本文将深入探讨这两种电阻的工作原理、区别以及在实际电路中的应用。

拉电阻和下拉电阻的主要作用是稳定信号电平。在数字电路中,信号通常处于高电平(1)或低电平(0)两种状态。然而,在某些情况下,信号可能会处于“浮空”状态,即既不是高电平也不是低电平,这种状态可能导致电路工作不稳定。拉电阻和下拉电阻就是用来解决这个问题的。

拉电阻的工作原理是通过与电源串联,将信号线的电平拉高至接近电源电压。以一个典型的按键电路为例,每个按键都连接一个上拉电阻。当按键未按下时,上拉电阻将IO口的电平稳定在高电平状态。当按键按下时,IO口被拉低至低电平。这种设计可以确保在按键未按下时,IO口始终处于可预测的高电平状态,从而避免了因信号浮空而产生的误操作。

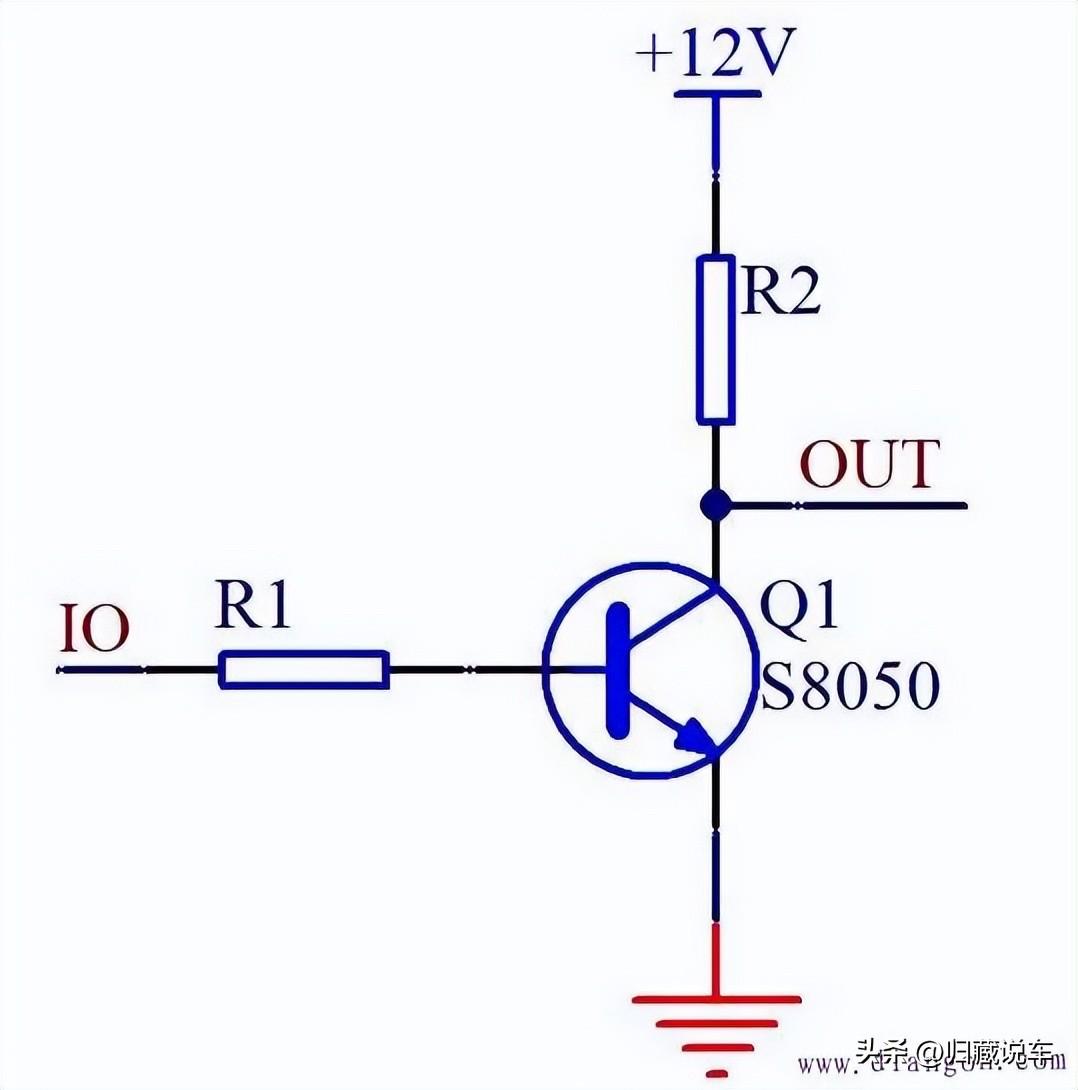

下拉电阻的工作原理则恰恰相反。它通过与地(GND)串联,将信号线的电平拉低至接近地电平。在某些电路中,下拉电阻可以用来确保信号在未被驱动时保持在低电平状态。例如,在一个三极管或场效应管的控制极,下拉电阻可以确保在没有外部信号输入时,管子处于截止状态。

拉电阻和下拉电阻的主要区别在于它们连接的对象不同。拉电阻通常与电源相连,用于将信号拉高至高电平;而下拉电阻则与地相连,用于将信号拉低至低电平。在实际应用中,选择使用哪种电阻取决于电路的具体需求。

在实际应用中,拉电阻和下拉电阻的应用非常广泛。除了前面提到的按键电路,它们还常用于总线驱动、信号隔离、防抖动等场合。例如,在一个I2C总线系统中,上拉电阻用于确保总线在未被驱动时保持高电平,从而避免了信号冲突。在一些敏感的模拟信号电路中,下拉电阻可以用来降低噪声干扰,提高信号的稳定性。

总的来说,拉电阻和下拉电阻在数字电路设计中扮演着至关重要的角色。它们不仅能够稳定信号电平,防止误操作,还能提高电路的整体性能和可靠性。对于电路设计工程师来说,熟练掌握这两种电阻的特性和应用,是设计出稳定可靠数字电路的基础。