什么是JESD204标准,为什么我们要重视它?

发布时间:2024-09-18

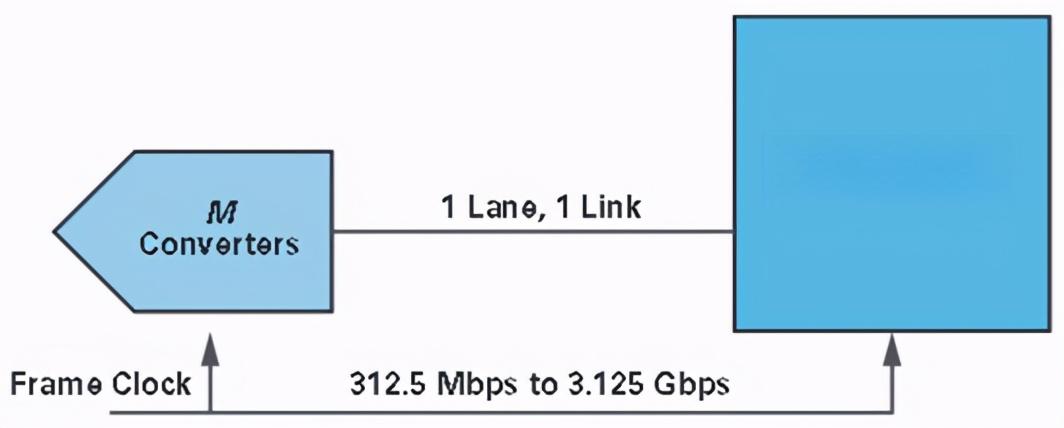

JESD204标准是由JEDEC固态技术协会制定的高速串行接口规范,主要用于高速数据转换器(如模数转换器ADC和数模转换器DAC)与逻辑器件(如FPGA或ASIC)之间的数据传输。自2006年发布以来,JESD204标准经历了多次更新和完善,目前最新的版本为JESD204B。

JESD204标准的诞生源于对更高效率转换器接口的需求。随着转换器分辨率和速度的提高,传统的互补金属氧化物半导体(CMOS)和低压差分信号(LVDS)接口已无法满足要求。JESD204接口通过提供更高的数据传输速率、更少的引脚数和更小的封装尺寸,显著提升了转换器的性能和效率。

从JESD204到JESD204B的演进过程中,标准经历了几个关键的改进:

-

数据速率的提升:JESD204B支持的通道数据速率从最初的3.125 Gbps提高到了12.5 Gbps,并将器件划分为三个不同的速度等级。

-

确定性延迟的引入:JESD204B规范定义了三种器件子类,其中子类1和子类2支持确定性延迟,这对于确保转换器正确重建模拟信号至关重要。

-

器件时钟的使用:JESD204B版本采用器件时钟而非帧时钟,为系统设计提供了更大的灵活性。

-

多通道支持:JESD204B增加了对多路对齐串行通道的支持,满足了高采样速率和高分辨率转换器的需求。

JESD204B标准的关键优势在于:

-

高效的数据传输:通过串行化数据,JESD204B接口大大减少了所需的引脚数。例如,对于一个200 MSPS的转换器,使用JESD204B接口的CML驱动器只需2个引脚,而传统的CMOS和LVDS接口则需要12个和13个引脚。

-

低功耗:JESD204B接口规范要求降低峰峰值电压水平,随着采样速率的提高,这有助于降低功耗。

-

灵活的系统设计:使用器件时钟作为主要时钟源,简化了系统设计的复杂性。

JESD204B标准在高速数据转换器领域的应用前景广阔。随着5G通信、高性能计算和自动驾驶等新兴技术的发展,对高速、高分辨率数据转换器的需求将持续增长。JESD204B标准能够满足这些应用对数据传输带宽和效率的要求,有望成为未来转换器数字接口的行业标准。

然而,在实施JESD204B标准的过程中,也面临着一些挑战:

-

缺乏官方兼容性测试规范:与其他高速串行接口标准不同,JESD204B标准没有官方的兼容性测试规范,这给系统设计人员带来了额外的测试和验证工作。

-

物理层测试的复杂性:JESD204B PHY测试涉及多种测试项目,包括抖动、眼图模板等,需要仔细理解和执行。

-

加重和均衡的设置:在实际应用中,需要根据PCB走线的插入损耗来调整加重和均衡的设置,以确保信号的完整性。

尽管存在这些挑战,JESD204B标准凭借其卓越的性能和灵活性,正在成为高速数据转换器领域的主流接口标准。随着技术的不断进步和标准的进一步完善,JESD204B有望在未来的数据转换器设计中发挥更加重要的作用。