芯片制程的物理和工程极限究竟在哪里?1nm是摩尔定律的尽头?

发布时间:2024-09-18

芯片制程工艺正在逼近物理极限。2022年,台积电和三星已经实现了3nm工艺的量产,而2nm工艺的研发也已提上日程。然而,随着晶体管尺寸不断缩小,1nm这个关键节点正引发业界的广泛关注和讨论。

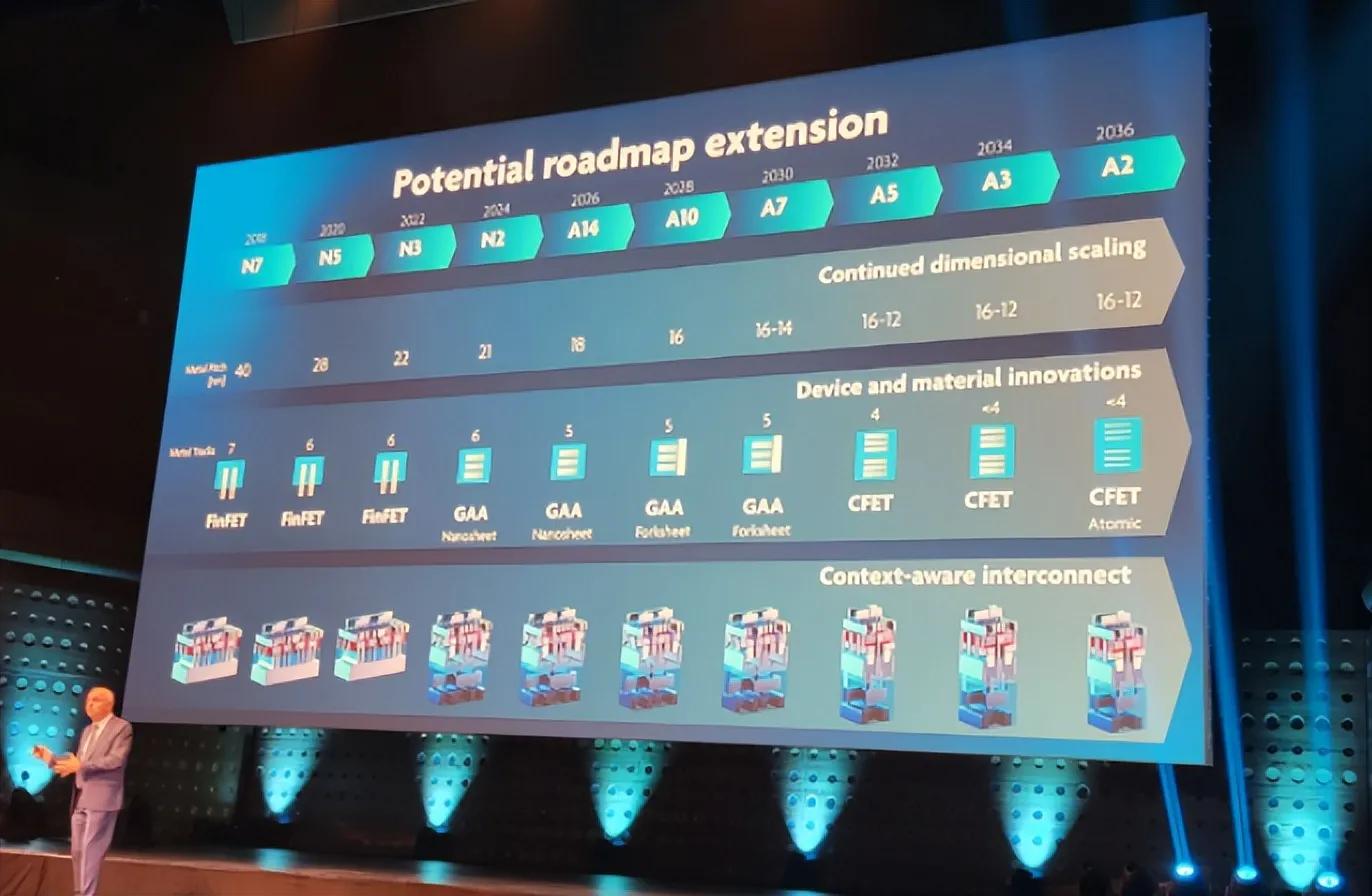

1nm制程面临着严峻的物理和工程挑战。当晶体管尺寸缩小到1nm时,量子隧穿效应将变得尤为显著。正如比利时微电子中心(IMEC)在FUTURE SUMMITS 2022大会上展示的路线图所示,要达到1nm制程还需6年时间,而到2036年,芯片制程甚至可能突破到0.2nm。但这一预测也引发了质疑。美国劳伦斯·伯克利国家实验室的研究团队已经成功研制出栅极仅长1纳米的晶体管,这似乎预示着1nm制程并非遥不可及。

然而,摩尔定律是否会在1nm处失效?这个问题在业界引发了广泛讨论。摩尔定律预测,集成电路上可容纳的晶体管数目每隔18-24个月就会翻一番。这一规律在过去几十年里得到了惊人的一致验证。但随着芯片制程逼近1nm,量子效应开始显现,电子不再严格遵循欧姆定律,而是可能穿越计算单元之间的壁垒,导致计算错误。这无疑给摩尔定律的持续有效性蒙上了阴影。

尽管如此,业界并未放弃对更小制程的追求。台积电、英特尔和三星等巨头仍在投入巨资研发更先进的制程技术。台积电的2nm工艺已经取得重大突破,采用了全新的多桥通道场效晶体管(MBCFET)架构。这表明,即使在面临物理极限的情况下,工程师们仍在寻找突破的方法。

面对1nm制程的挑战,芯片技术的发展正朝着多个方向探索。新材料的应用是一个重要方向。除了传统的硅材料,砷化镓(GaAs)、磷化铟(InP)等第二代半导体材料正在得到更多关注。2021年,台大、台积电和麻省理工共同发布研究成果,提出利用半金属铋(Bi)作为二维材料的接触电极,这不仅能大幅降低电阻和提高电流,还能有效减少量子隧穿效应的影响。

此外,三维制造工艺和新器件结构也在积极探索中。碳纳米管、纳米线等新型材料的应用,有望进一步解决当前芯片面临的问题。这些创新不仅可能突破1nm制程的物理限制,还可能为芯片技术开辟全新的发展方向。

尽管1nm制程面临诸多挑战,但芯片技术的发展前景依然广阔。正如摩尔定律的提出者戈登·摩尔所言,技术进步往往超出我们的预期。随着新材料、新架构的不断涌现,芯片技术很可能会在突破1nm之后继续演进。这不仅将推动计算机和移动设备性能的持续提升,还将为人工智能、量子计算等前沿领域的发展提供强大支撑。

1nm是否是摩尔定律的尽头?这个问题的答案或许并不重要。重要的是,人类对技术创新的追求永无止境。无论1nm之后的道路如何,芯片技术的发展必将持续推动整个科技行业的进步,为人类社会带来更多的可能性。